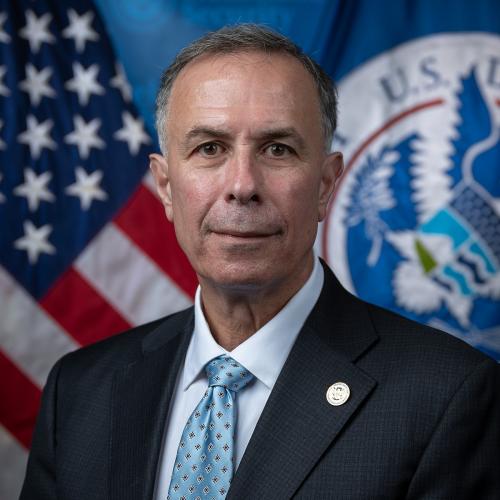

Dr. Dimitri Kusnezov [Kooz-NETS-off] was confirmed as the Under Secretary for the Science and Technology Directorate (S&T) on September 8, 2022. As the science advisor to the Homeland Security Secretary, Dr. Kusnezov heads the research, development, innovation and testing and evaluation activities in support of the Department of Homeland Security’s (DHS) operational Components and first responders across the nation. S&T is responsible for identifying operational gaps, conceptualizing art-of-the-possible solutions, and delivering operational results that improve the security and resilience of the nation.

Prior to DHS, Dr. Kusnezov was a theoretical physicist working at the U.S. Department of Energy (DOE) focusing on emerging technologies. He served in numerous positions, including the Deputy Under Secretary for Artificial Intelligence (AI) & Technology where he led efforts to drive AI innovation and bring it into DOE missions, business and operations, including through the creation of a new AI Office.

Dr. Kusnezov has served in scientific and national security positions, including Senior Advisor to the Secretary of Energy, Chief Scientist for the National Nuclear Security Administration, Director of Advanced Simulation and Computing and the Director of the multi-billion-dollar National Security Science, Technology and Engineering programs. He created numerous programs, including for Minority Serving Institutions, international partners, private sector and philanthropic entities. He has worked across agencies to deliver major milestones such as DOE’s 10-year grand challenge for a 100 Teraflop supercomputer, and first of their kind and world’s fastest supercomputers.

Prior to DOE and his pursuit of public service, Dr. Kusnezov had a long career in academia where he published more than 100 articles and edited two books. He joined Yale University faculty where he was a professor for more than a decade in Theoretical Physics and served as a visiting professor at numerous universities around the world. Before this post, Dr. Kusnezov did a brief postdoc and was an instructor at Michigan State University, following a year of research at the Institut fur Kernphysik, KFA-Julich, in Germany. He earned his MS in Physics and Ph.D. in Theoretical Nuclear Physics at Princeton University and received Bachelor of Arts degrees in Physics and in Pure Mathematics with highest honors from UC Berkeley.